AMD CEO Lisa Su(苏姿丰)出席了imec的ITF World 2024大会,接受了享有盛誉的imec创新奖,以表彰其创新和行业领导力,戈登·摩尔(Gordon Moore)、比尔·盖茨(Bill Gates)也曾获此奖项。

在苏姿丰的演讲中,她介绍了AMD为实现公司30x25目标所采取的策略,该目标旨在到2025年将计算节点的能效提高30倍。苏姿丰宣布,AMD不仅有望实现这一目标,而且现在还找到了2026年至2027年将能效提高100倍以上的办法。

由于ChatGPT等生成式AI LLM的激增,人们对AI功耗的担忧成为关注的焦点,AMD早在2021年就预见到了AI巨大的功耗需求所带来的问题。当时,AMD开始致力于其30x25目标,以提高数据中心计算节点的能效,特别指出AI和HPC的功耗是一个迫在眉睫的问题。

随着训练模型所需的计算量增加,AI功耗问题只会愈演愈烈。苏姿丰指出,第一批图像和语音识别人工智能模型的大小过去每两年翻一番,与过去十年计算能力的进步速度基本一致。然而,生成式人工智能模型的规模现在以每年20倍的速度增长,超过了计算和存储进步的速度。苏姿丰表示,随着大模型可能很快就需要数十万个GPU进行训练,单个大模型一次训练需要的需要的电力多达几吉瓦时。

AMD为提高能效制定了多管齐下的策略,包括一种广泛的方法,从其硅架构和先进的封装策略扩展到AI特定的架构、系统和数据中心级调整以及软件和硬件共同设计计划。

当然,硅是基石。苏姿丰指出,3nm全栅极(GAA)晶体管是AMD在硅路线图上的下一步,旨在提高功率效率和性能,同时继续关注先进封装和互连,以实现更节能、更具成本效益的模块化设计。先进封装在扩展设计以在单芯片封装的限制内提升性能方面发挥着关键作用,AMD采用2.5D和3D封装的混合技术,以最大限度地提高每平方毫米数据中心硅片的计算能力。

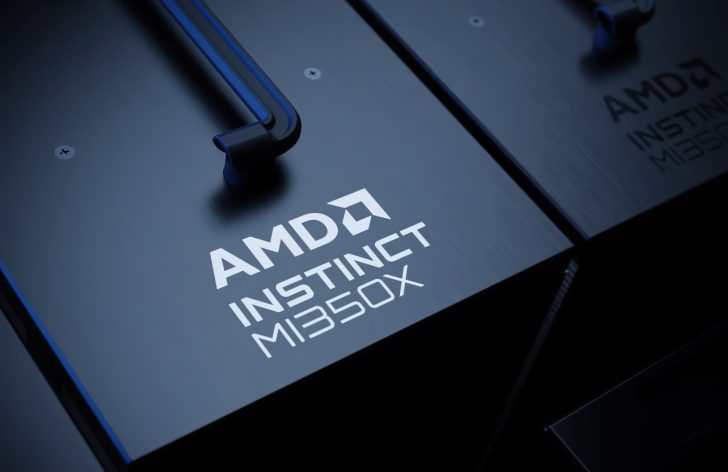

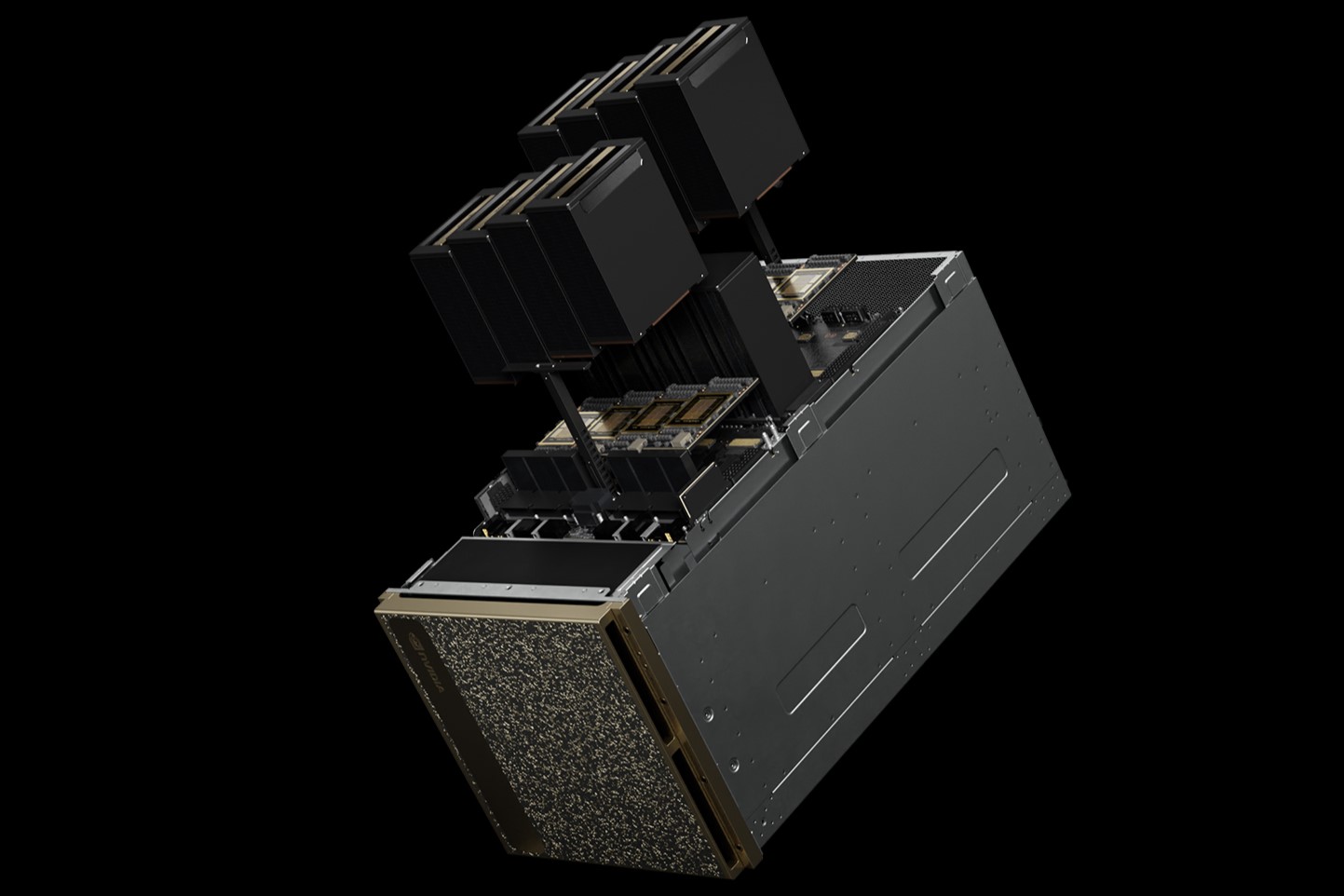

在服务器节点和服务器机架之间传输数据会因距离较长而消耗额外电力,因此优化数据局部性可以节省大量电力。AMD的MI300X体现了制造越来越大的芯片封装所带来的效率——该芯片拥有1530亿个晶体管,分布在12个芯片上,搭配24个HBM3芯片,可提供192GB的存储容量,所有这些都可作为本地内存供GPU使用。再加上封装内单元之间经过功率和性能优化的Infinity Fabric互连,极高的计算和存储密度可将更多数据保持在靠近处理核心的位置,从而减少传输数据所需的能量。(校对/孙乐)

登录

登录